AV-870p PCle Adaptive SoC Card

# **Versal™ Premium Adaptive SoC Card**

400G and PCle Gen5

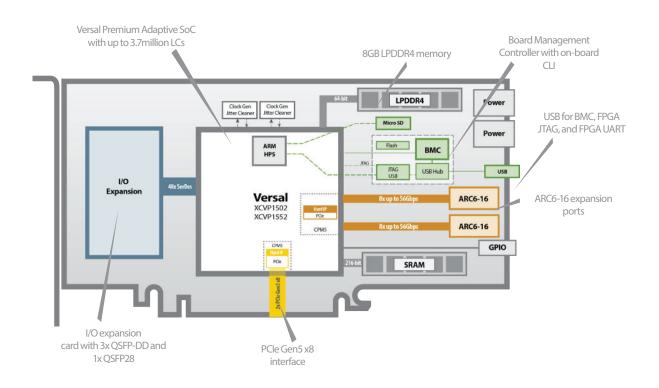

Brought to market in partnership with LDA Technologies, the AV-870p is a PCIe Gen5 accelerator card designed to deliver extreme performance for data center and edge compute workloads. Featuring AMD Xilinx®'s Versal Premium Adaptive SoC, the AV-870p is a deployment-ready full height, ¾ length PCIe accelerator compatible with high-performance servers. The card features QSFP-DDs for up to 6x 400G, 2x PCIe Gen5 x8, and a sophisticated Board Management Controller (BMC) for advanced system monitoring and control.

key features

QSFP-DDs and QSFP28 for **6x 400G**

2x PCle Gen5 x8 Versal Premium with up to 3.7M Logic Cells

## **Additional Services**

Take advantage of BittWare's range of design, integration, and support options

**Customization**

Additional specification options or accessory boards to meet your exact needs.

#### **Server Integration**

Available pre-integrated in our <u>TeraBox servers</u> in a range of configurations.

#### **IP and Solutions**

Our portfolio of IP and solutions reduce risk for development and deployment.

#### **Service and Support**

BittWare Developer Site provides online documentation and issue tracking.

### **Board Specifications**

| Adaptive SoC       | <ul><li>Versal Premium</li><li>VP15 02/ VP1552</li><li>Core speed grade - 2</li></ul>                                                                                                                                                                   |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On-board Flash     | Flash memory for booting FPGA                                                                                                                                                                                                                           |

| External memory    | 2x 4GB LPDDR4 chips (8GB total) @ 4266MHz for ARM system (64 bits)     432 MB of ultra-low-latency GSI SRAMs     12x 18-bit chips     216-bit total bus width                                                                                           |

| Host interface     | 2x PCle x8 Gen5 interfaces direct to FPGA, con-<br>nected to PCle Hard IP                                                                                                                                                                               |

| I/O Expansion Site | I/O expansion site connected to FPGA via 48x SerDes channels:  VP1502:12 GTYP and 36 GTM  VP1552: 32 GTYP and 16 GTM  Default I/O module features:  2x QSFP-DD cages on front panel supporting 56G PAM4,  QSFP28 cage on front panel supporting 28G NRZ |

| Clocking           | 2x Jitter cleaners for network recovered clocking                                                                                                                                                                                                       |

| ARC6-16            | 2x ARC6-16 connectors connected to FPGA via 8x SerDes channels each (16x total)     VP1502: 16x GTM 56Gbps channels     VP1552: 16x GTYP 32Gbps channels                                                                                                |

| USB                | USB access to BMC, USB-JTAG, USB-UART                                                                                                                                                                                                                   |

| Board<br>Management<br>Controller | <ul> <li>Onboard CLI</li> <li>Python, C++ API</li> <li>200 Mbps parallel port connected to the FPGA fabric and the NO</li> <li>USB SD Card Reader for simple OS images transfer to ARM processors</li> <li>Fast FPGA Boot Flash programming</li> <li>Temperature, voltage, current monitoring</li> <li>SNMP agent for centralized management</li> <li>Dedicated preprogrammed array of 32 MAC addresses</li> <li>I/O ports monitoring. Full QSFP, SFP, QSFP-DD access</li> <li>and programming through CLI and API</li> <li>CLI-based clock selection supporting custom clock configurations</li> </ul> |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cooling                           | Standard: dual-width passive heatsink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Electrical                        | <ul> <li>On-board power derived from 12V PCle slot and 2x<br/>AUX connectors</li> <li>Power dissipation is application dependent</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Environmental                     | Operating temperature 5°C to 35°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Form factor                       | ¾-length, standard-height PCle dual-width board     10 x 4.37 inches (254 x 111.15 mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### **Development Tools**

| Application |

|-------------|

| developmen  |

Supported design flows -Vivado Design Suite (HDL, Verilog, VHDL, etc.)

Rev 2023.11.20 | November 2023

International Distributors

Sky Blue Microsystems GmbH Geisenhausenerstr. 18 81379 Munich, Germany +49 89 780 2970, info@skyblue.de www.skyblue.de

In Great Britain:

Zerif Technologies Ltd.

Winnington House, 2 Woodberry Grove

Finchley, London N12 0DR

+44 115 855 7883, info@zerif.co.uk

www.zerif.co.uk